芯動(dòng)科技資(zī)深營銷經理韓輝表示,在變化莫測的高科技市場中(zhōng),高端芯片投資(zī)大、風險高,設計企業(yè)需要選擇量産經驗豐富、貼近客戶需求、定制能力強且能兜底風險的IP提供商(shāng),幫助産品實現強競争力和(hé)持久生命力。芯動(dòng)科技作為一站(zhàn)式IP賦能型領軍企業(yè),深耕高速接口17年,始終秉持着“客戶的成功就是我們的成功”理念,與SoC企業(yè)緊密合作,提供高速接口IP的完整硬核解決方案和(hé)多種定制化合作模式。基于十多年先進工藝定制經驗和(hé)全球供應鍊能力,芯動(dòng)科技形成了涵蓋體系架構、總線/内核拼接、IP集成/SoC集成能力,從IP到驗證、從設計到量産、從芯片到系統的全套芯片定制量産服務,以IP全棧能力和(hé)芯片定制為客戶最終産品賦能,合作模式靈活,可(kě)真正做到全流程加速和(hé)風險兜底,一站(zhàn)式幫助客戶解決問(wèn)題。

▲芯動(dòng)科技VP/技術(shù)總監高專分享芯動(dòng)科技VP/技術(shù)總監高專則詳細介紹了芯動(dòng)核心産品——高速接口IP“三件套”,包括高端DDR系列、兼容UCIe标準的Innolink™ Chiplet系列、高速SerDes系列,全面覆蓋各大代工廠55nm到5nm工藝節點,可(kě)根據用戶的應用場景提供差異化定制方案,在全球範圍内均已大規模商(shāng)用落地。芯動(dòng)全系列高端DDR IP解決方案,包括GDDR6/6X、HBM3/2e、LPDDR5/5X/4/4X、DDR5/4等,全面支持JEDEC各标準,均包含物理層和(hé)控制器(qì)IP,提供高帶寬、高性能、低功耗的一站(zhàn)式交鑰匙方案,在全球範圍内實現了對DDR接口技術(shù)的最全覆蓋。芯動(dòng)多标準高速SerDes支持28/32 & 56/64Gbps以内的各種串口協議,如(rú)PCIe6/5、PCIe4/3/2、USB4/3.x、SATA3.1/SAS2.0、XAUI/RXAUI、SGMII/HISGMII、QSGMII、RapidIO、JESD204B/C、CEI SR/MR/LR 25/56G+等,具有低功耗、低成本、零風險、快速響應、易于集成等特點,下(xià)一代ADC DSP based 112G PAM-4SerDes也在全力研發中(zhōng)并擇時推出。芯動(dòng)Innolink™ Chiplet IP支持矽基闆、有機物基闆和(hé)PCB闆三種互連模式,提供物理層方案以及PHY & Controller打包方案,還提供封裝設計、可(kě)靠性驗證、信号完整性分析、DFT、熱仿真、測試方案等全棧式服務,已經開發和(hé)疊代3年多的Innolink™ B/C技術(shù)還與去年發布的UCIe國際标準基本一緻,該方案已在芯動(dòng)自研“風華1号”GPU以及多個(gè)第三方客戶的智能處理SoC中(zhōng)成功實現商(shāng)用量産。

▲知存科技COO兼研發副總裁殷積磊分享

知存科技COO兼研發副總裁殷積磊分享了存算一體芯片的發展和(hé)落地應用。存算一體是一種新型計算架構,核心是将存儲和(hé)計算融合在一起,突破馮·諾依曼架構瓶頸,減少(shǎo)數據來回搬運的過程,實現計算能效數量級提升,在人工智能、雲計算、邊緣計算等領域應用前景廣闊。知存科技擁有業(yè)内領先的存算一體技術(shù),具備多種适合存内計算的非易失性存儲器(qì)工藝研發經驗,構建了WTIN Mapper編譯器(qì)、工具鍊、存内計算電路(lù)設計、多核運算等完善的存算一體開發生态。基于自研MemCore技術(shù),知存科技針對端側AI計算市場打造了全球首顆存内計算SoC芯片,具備大算力、高能效、低功耗、多應用等優勢,AI算力相較于可(kě)穿戴設備現有芯片有數十倍到百倍的提升。

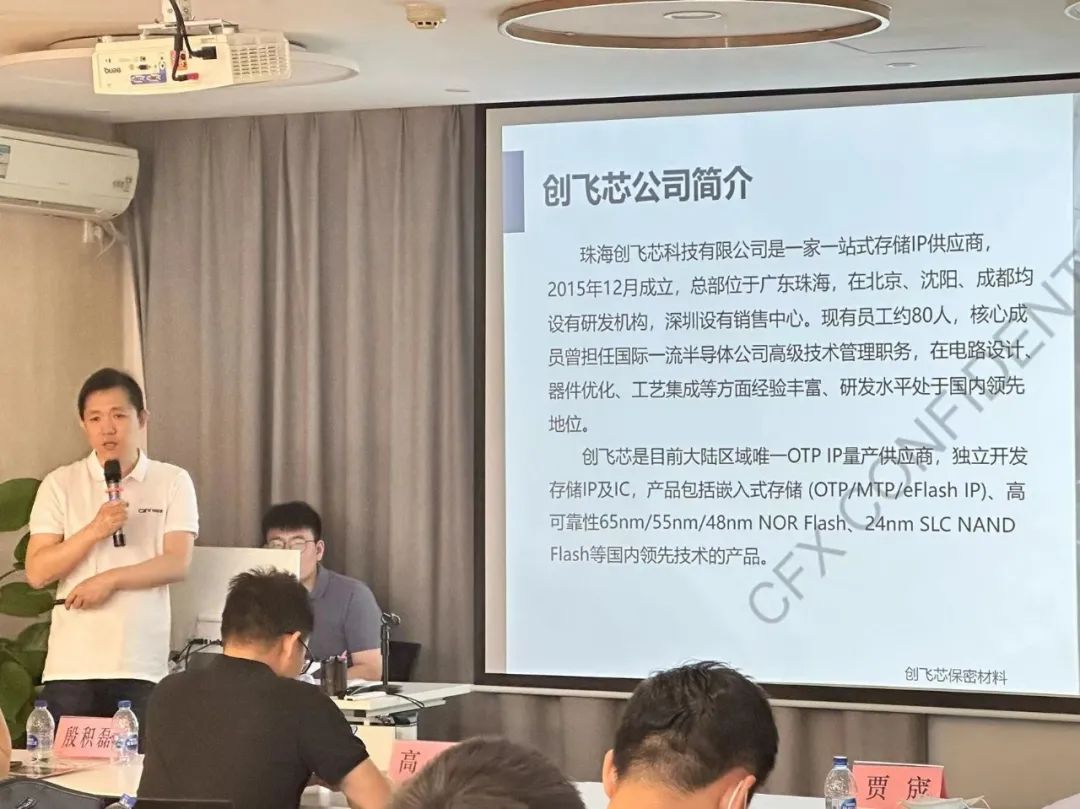

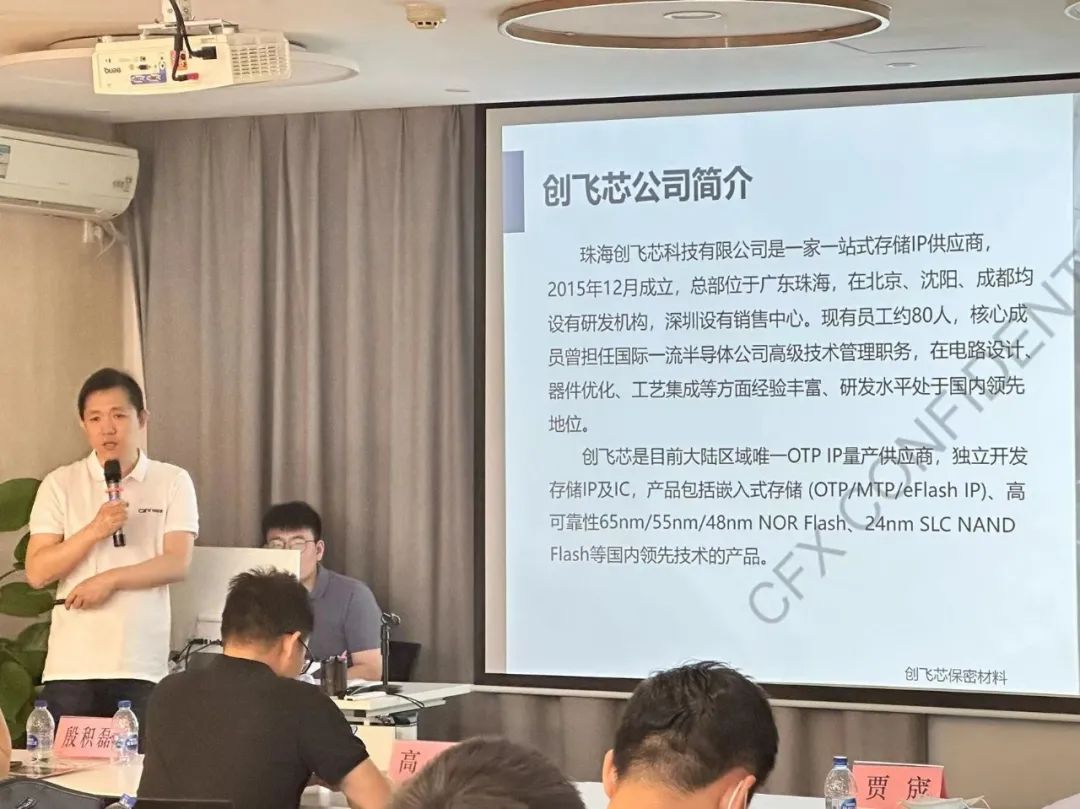

▲創飛芯科技工藝總監賈宬分享

創飛芯科技工藝總監賈宬深入介紹了公司明星産品——與标準CMOS工藝完全兼容的嵌入式OTP IP核。在100%CMOS工藝兼容、完全定制設計、OTP核面積更小、超高可(kě)靠性、卓越性能五大核心優勢的加持下(xià),OTP IP核已在不同世代CMOS邏輯/高壓工藝驗證 (0.18/0.16/0.13/0.11um及90/65/55/40/28/22/12/7nm),可(kě)在無需增加工藝步驟及光刻掩模版數量,無需開發專用工藝或器(qì)件條件下(xià),直接應用于其它類似CMOS工藝例如(rú)混合模式、射頻、 模拟、高壓、CMOS圖像傳感器(qì)和(hé)嵌入式Flash或EEPROM存儲器(qì)工藝,是公司最為核心和(hé)體現技術(shù)實力的産品之一。

在研讨會現場,與會代表與演講嘉賓針對高端IP應用、芯片安全風險控制、芯片項目合作等産業(yè)鍊關(guān)注的前沿問(wèn)題進行了深入地交流和(hé)探讨。未來,芯動(dòng)科技将會繼續攜手相關(guān)産業(yè)協會機構陸續舉辦相關(guān)研讨會,營造開放的技術(shù)讨論氛圍,促進合作的機會,激發新想法和(hé)新思考,為中(zhōng)國集成電路(lù)産業(yè)發展貢獻力量。

官方公衆号

官方公衆号 招聘公衆号

招聘公衆号