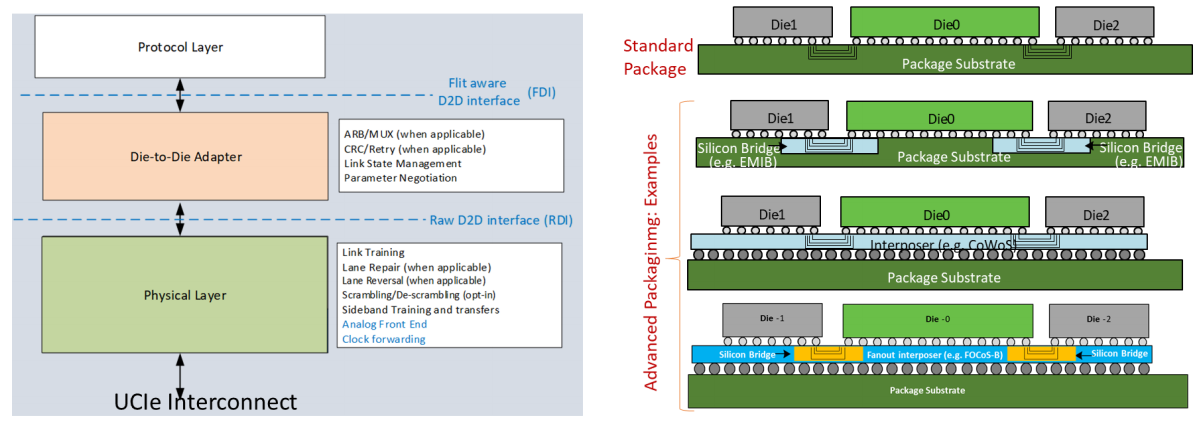

加入UCIe聯盟,首發UCIe Chiplet IP,芯動(dòng)科技獨領風騷Chiplet技術(shù)對當前突破AI和(hé)CPU/GPU等計算芯片的算力瓶頸具有重要戰略意義,設計靈活、成本低、上市周期短(duǎn),能夠滿足包括雲端、邊緣端、企業(yè)級、5G、汽車(chē)、高性能計算和(hé)移動(dòng)設備等在内的整個(gè)計算領域,對算力、内存、存儲和(hé)互連日益增長的高需求。此前,全球十大行業(yè)巨頭組成了UCIe(Universal Chiplet Interconnect Express)産業(yè)聯盟,攜手推動(dòng)Chiplet接口規範的标準化。作為在Chiplet互聯技術(shù)領域耕耘多年并率先成果産業(yè)化的IP領軍企業(yè),芯動(dòng)科技是國内首批加入該聯盟的廠商(shāng)之一。芯動(dòng)科技Chiplet架構師(shī)高專認為,“Chiplet聯盟的成立将形成開放互連的局面,統一标準将實現更強的賦能。但想要制定标準必須有領先的技術(shù)以及足夠的銷量,國内在這方面比較薄弱,加入UCIe産業(yè)聯盟是芯動(dòng)緻力于推動(dòng)Chiplet商(shāng)用進程、提高國内企業(yè)在Chiplet市場聲量的重要一步。”▲多芯粒互聯的Chiplet技術(shù)是實現高性能異構系統的發展趨勢

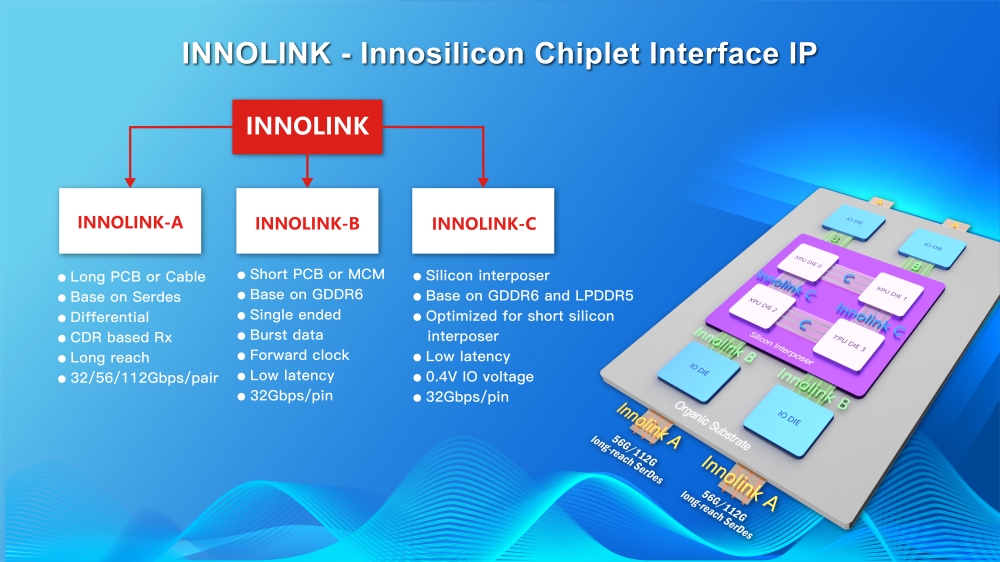

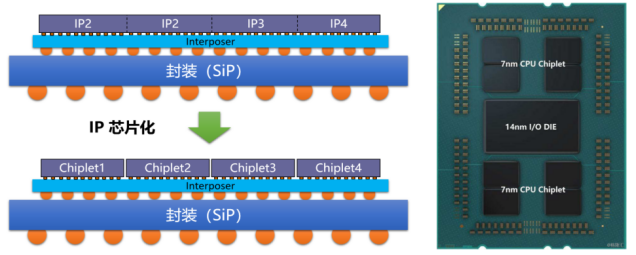

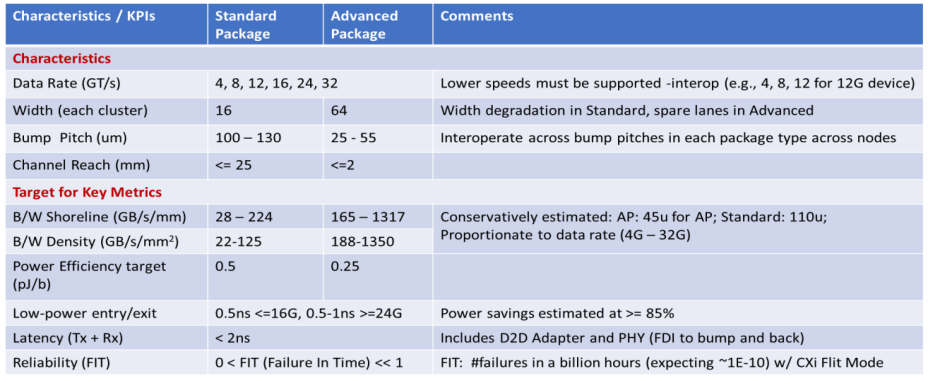

近年來,Chiplet概念開花(huā)結果,AMD、蘋果和(hé)英偉達等國際巨頭都發布了标志性的Chiplet旗艦産品,并在各個(gè)應用領域取得極大成功。國内上下(xià)遊企業(yè)也将之視為傳統半導體産業(yè)鍊重構的新機遇,諸多廠商(shāng)正積極開發相關(guān)産品,然而商(shāng)用成果寥寥無幾。芯動(dòng)科技可(kě)謂一枝獨秀。在UCle标準推出後不到三周,芯動(dòng)科技就宣布率先推出國産自主研發物理層兼容UCIe國際标準的IP解決方案-Innolink™ Chiplet,這是國内首套跨工藝、跨封裝的Chiplet連接解決方案,且已在先進工藝上量産驗證成功,俨然成為全球Chiplet市場的一顆亮(liàng)眼新星,也成為芯動(dòng)加入國際UCIe标準制定的敲門磚。

官方公衆号

官方公衆号 招聘公衆号

招聘公衆号