引言

高速SerDes主題頻頻出現在半導體論壇上,成為各大專場的熱點名詞,我們從技術(shù)發展和(hé)行業(yè)應用的角度來讨論一下(xià),SerDes技術(shù)為什麼這麼重要!

半導體技術(shù)的發展點亮(liàng)了一個(gè)新的數字時代,5G通(tōng)信、自動(dòng)駕駛、人工智能、大數據存儲、雲計算、高性能圖像媒體處理、萬物互聯、摩爾定律新延續等等熱點應用,掀起了一場翻天覆地信息技術(shù)革命,而這些應用在不斷攀登速率最高峰時,離(lí)不開最基本的數據傳輸技術(shù)。

适應大數據時代數據處理的高效、高性能需求,一些高速接口應運而生,比如(rú)我們熟悉的PCI Express、USB3.0、XAUI萬兆以太網、SATA、DP、RAPID IO、HBM。而這些高速接口的底層都是基于Serdes技術(shù),因此我們将從SerDes的視角來揭開這些熱點技術(shù)的面紗。

一、早期串行演變到并行通(tōng)信

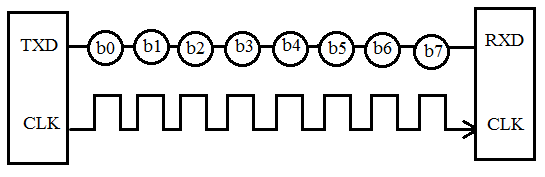

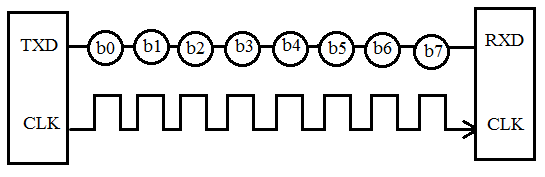

上世紀八十年代,計算機通(tōng)信領域數據傳輸以串行為主,它具有簡單、成本低廉的優勢,比如(rú)UART 20Kbps、 SPI 1Mbps,後來在一些總線通(tōng)信中(zhōng)逐漸改為使用并口通(tōng)信,比如(rú)我們常見的MII接口可(kě)以達到100Mbps左右。

串行通(tōng)信

并行通(tōng)信

并行接口用多根信号同時傳輸數據,在當時有效提高了整體數據傳輸效率,如(rú)早期的以太網MII、PCI總線技術(shù)以及最普遍的DDR内存通(tōng)信技術(shù)。

二、并行技術(shù)的發展和(hé)瓶頸

随着應用技術(shù)對速率的渴望越來越高,百Mbps級别的傳輸率已經難以滿足各種需求,比如(rú)5G的高速通(tōng)信、高分辨率的圖像處理、顯卡的數據應用、高性能的計算和(hé)服務器(qì),這些應用動(dòng)辄要求Gbps、GTs級别的速率,并口發展遇到嚴重瓶頸。

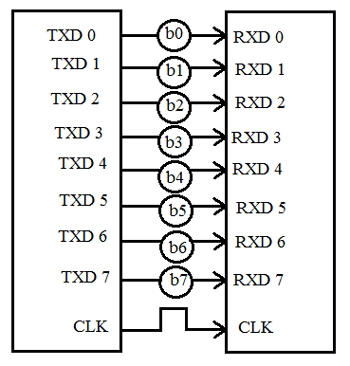

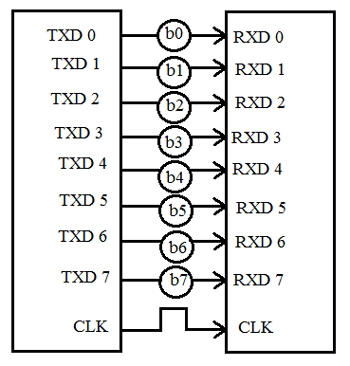

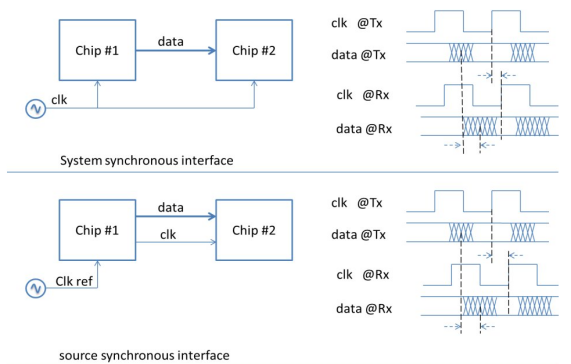

系統同步和(hé)源同步時鐘的并行通(tōng)信

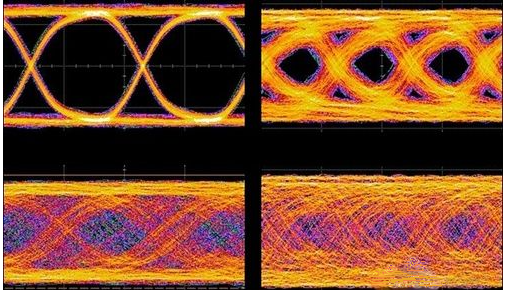

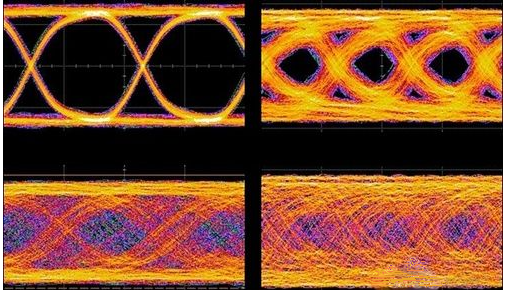

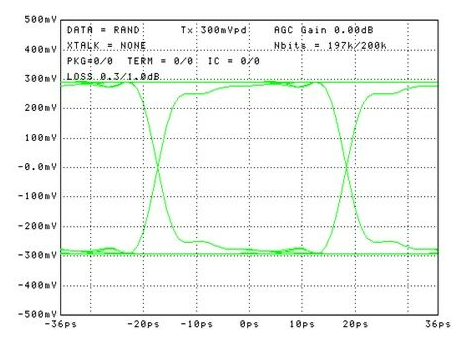

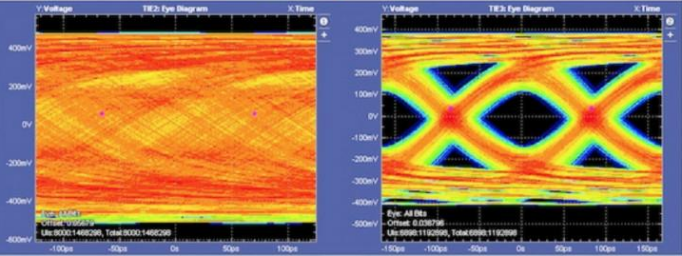

随着速率增加信号的眼圖逐漸模糊

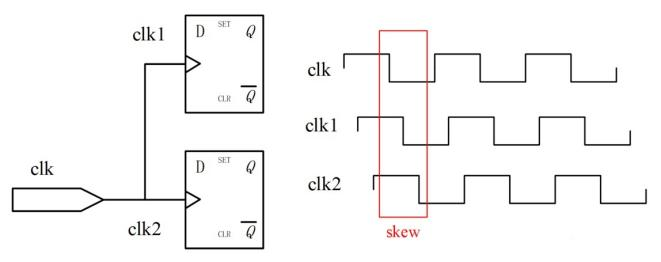

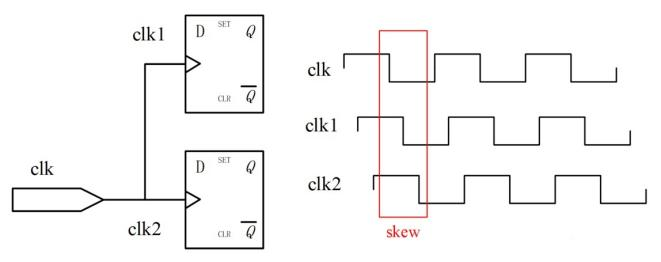

采用并行通(tōng)信時,我們需要考慮時鐘傾斜和(hé)抖動(dòng)引起的信号衰減,舉個(gè)簡單的例子(zǐ),10個(gè)人并排走,速度越快,就越難以對齊并排,在術(shù)語上為Clock skew。

Clock Skew

Jitter

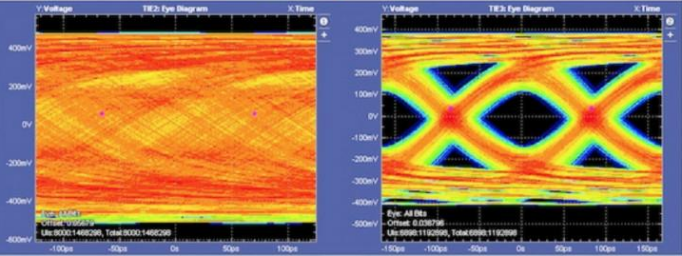

随着并行速率的增加,時鐘抖動(dòng)受影響越來越嚴重,從示波器(qì)眼圖可(kě)以看到最後波形疊加十分嚴重,接收端已經完全無法識别有效信号了,并行通(tōng)信的發展瓶頸主要如(rú)下(xià):

· 兩個(gè)芯片間的時鐘傳播延時(clock skew)

· 并行數據各個(gè)bit的傳播延時 (data skew)

· 時鐘和(hé)數據的傳播延時不一緻(skew between data and clock)

· 多根同步信号在高速率時會發生串擾(共模傳輸、差模傳輸、靜态傳輸),而且繁多的信号很難在PCB并行通(tōng)信布線,要求等長、線寬間距一緻,layout的成本和(hé)難度很高,外部的連線也受到嚴重的限制,整個(gè)系統硬件成本高昂,系統的穩定性很難提高,舉個(gè)例子(zǐ),就像32個(gè)人并排向前走,速度越快,越容易互相踩踏。

總之,并行數據很難做到很高的傳輸效率,成本也越來越高昂,理解了上面skew的概念,我們來做一個(gè)小的計算來理解。

32bit數據的并行總線,傳輸的各種延遲skew都是較理想狀态時:

數據從發送端的skew = 100 ps

PCB走線引起的skew = 100 ps

時鐘的周期抖動(dòng)jitter = +/- 50 ps

接收端觸發器(qì)采樣窗口 = 200 ps

最理想并行的有效頻率 = 1/(100+100+100+200) = 2.0GHz (DDR)或者1.0GHz(SDR單邊沿).

在如(rú)此苛刻的優化硬件的條件下(xià),用32根信号外加各種時鐘和(hé)控制信号,有效頻率才做到2G左右,而常用的DDR4核心頻率基本是400~800MHz,可(kě)見并行通(tōng)信的邊際效益越來越低了。

三、高速串行SerDes 的關(guān)鍵技術(shù)

在遭遇了并行技術(shù)的嚴重瓶頸後,通(tōng)信領域工程師(shī)們又回過頭來想起了串行技術(shù)的好,與并行技術(shù)對比,串行技術(shù)有以下(xià)好處:

·IO的占用少(shǎo)

·布線簡單

·沒有信号間的串擾

·系統的硬件成本低

有讀者會問(wèn),通(tōng)信領域最早就是串行通(tōng)信,為何發展到并行通(tōng)信後,又重新發展串行通(tōng)信呢(ne)?這是因為近幾年一些關(guān)鍵技術(shù)的發展,幫助串行通(tōng)信突破了原有舊架構上的瓶頸。

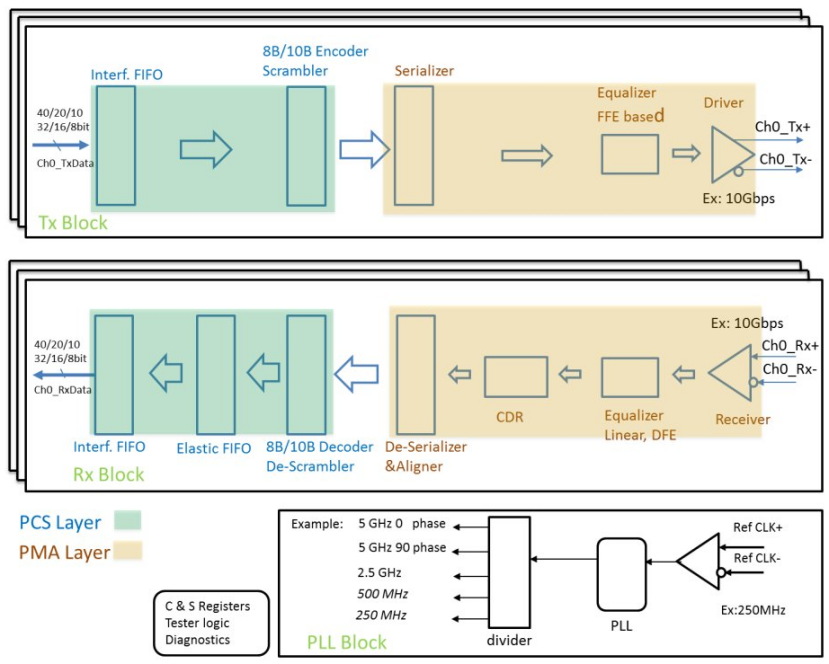

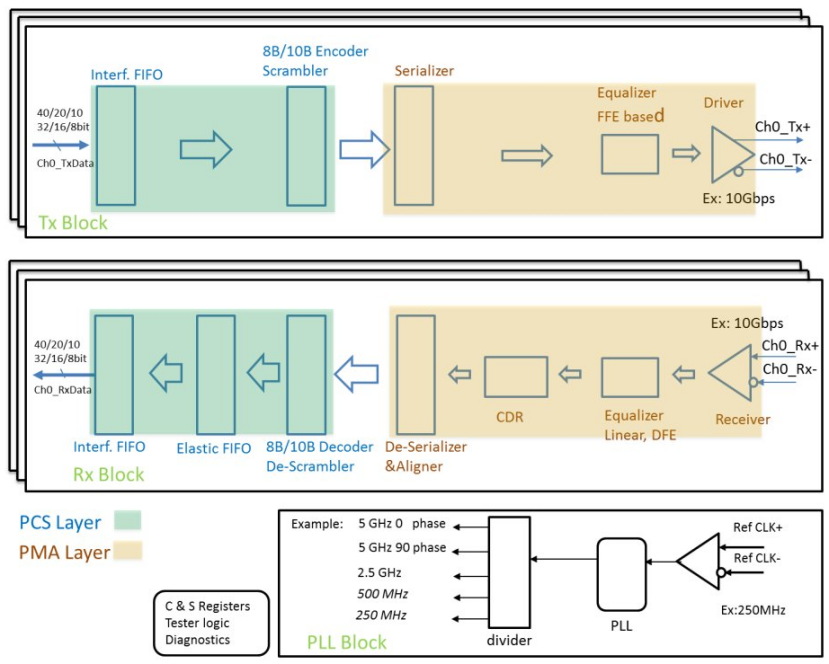

SerDes功能框圖

SerDes功能框圖

我們先從SerDes的基本功能來理解,SerDes是英文(wén)SERializer(串行器(qì))/DESerializer(解串器(qì))的簡稱 ,它包含了串化/解串器(qì)、均衡、FIFO、差分通(tōng)道、編碼器(qì)等主要功能模塊。

其中(zhōng)幾項關(guān)鍵的SerDes基礎技術(shù)促進了串行通(tōng)信效率的大幅度提高,我們将進行重點分析:

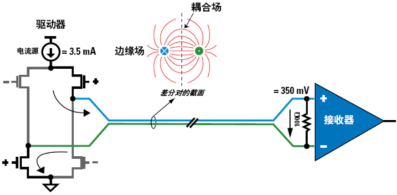

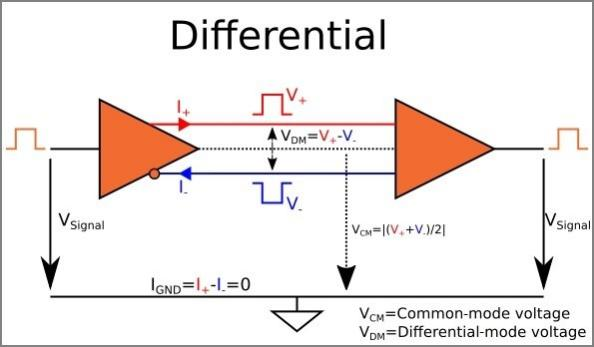

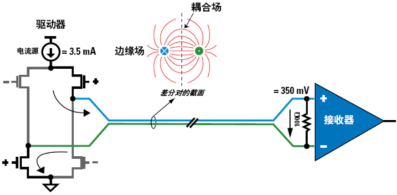

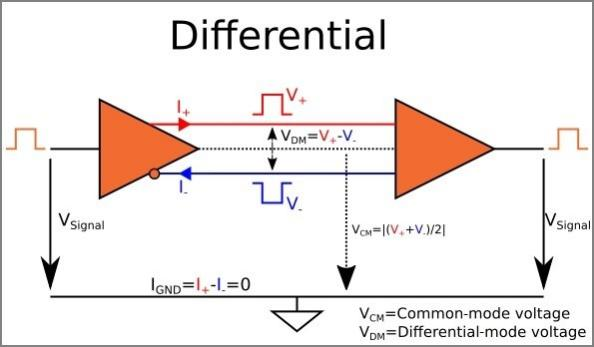

·差分通(tōng)信(differential signaling)

與傳統的單端通(tōng)信不同,差分信号由一對相反信号組成,接收端以兩者的絕對值來判斷信号。在傳輸過程中(zhōng),即使信号受到幹擾,也是同一方向上的,并不會改變兩者的絕對值,這樣就保持了傳輸信号的完整性。現在最新的接口技術(shù)如(rú)以太網、LVDS、MIPI、HDMI等都采用了差分通(tōng)信技術(shù)。

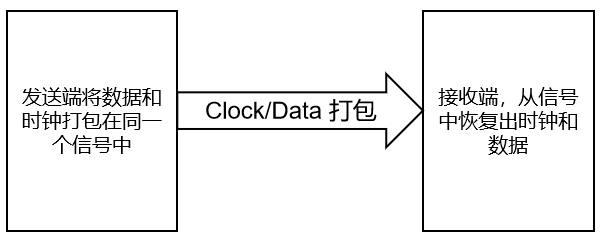

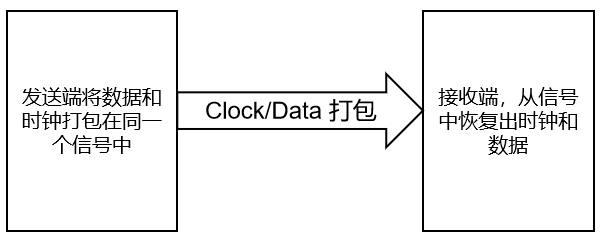

·時鐘恢複 CDR(Clock Data Recovery)

簡單來講,CDR技術(shù)就是把時鐘信号和(hé)數據信号打包在一個(gè)信号裡發送,到達接收端再解包,所以就沒有clock線,自然clock skew也沒有了,更不存在時鐘與數據的skew了,在上文(wén)的計算公式裡一下(xià)就少(shǎo)了200ps的延遲,這比之早期的源同步時鐘和(hé)系統同步時鐘是一個(gè)巨大的進步,CDR技術(shù)也稱為自同步技術(shù)。因為這個(gè)技術(shù)早期并沒有,所以限制了此前串行通(tōng)信的發展。

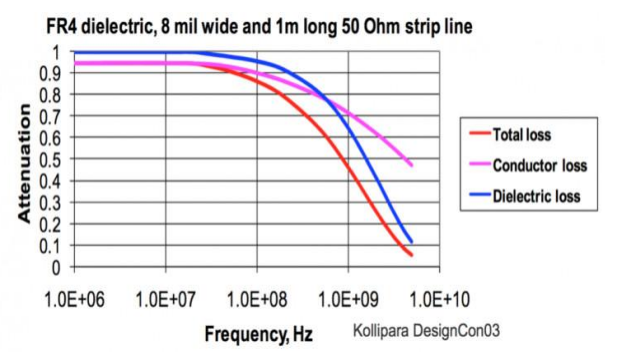

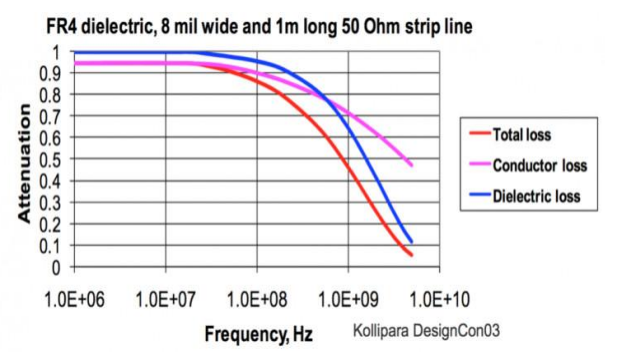

·均衡技術(shù)(Channel Equalization,Eq)

現實的信号傳輸通(tōng)道(芯片封裝,PCB走線和(hé)線纜)存在趨膚效應和(hé)介質不均勻,造成寄生電容和(hé)阻抗,導緻數據傳輸在高頻時有嚴重的衰減。

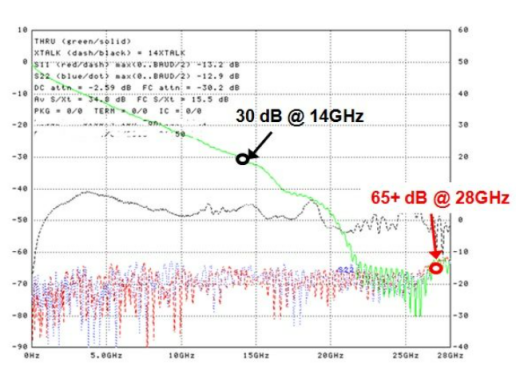

信号在 10^8HZ 開始嚴重的衰減

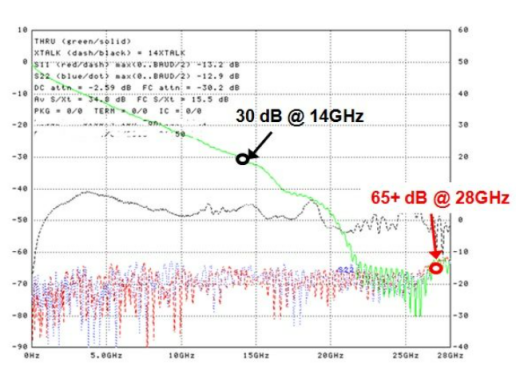

在 28Gbps 信号能量衰減 30db,電壓幅度隻剩 3%

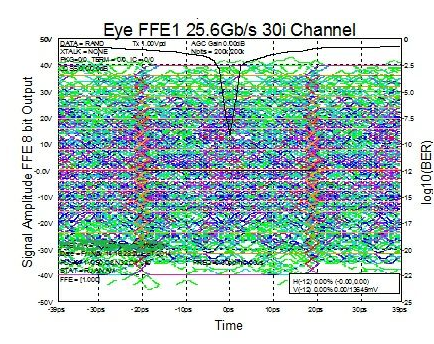

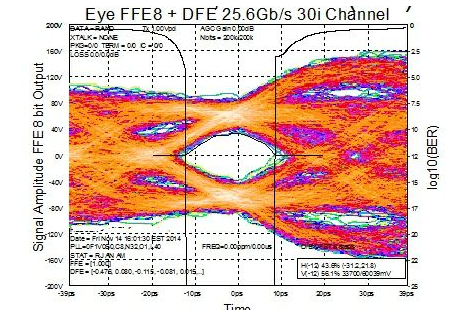

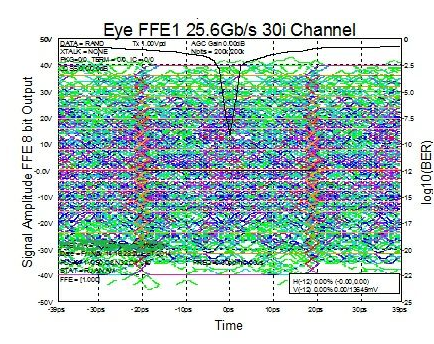

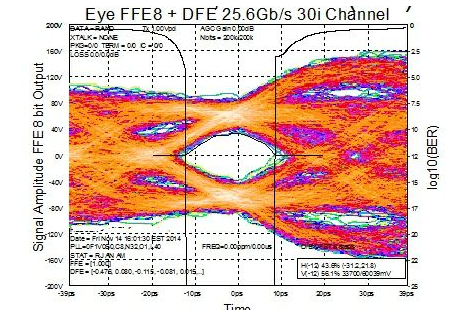

為了應對高頻信号的衰減,SerDes技術(shù)在接收端和(hé)發送端都有通(tōng)道均衡Equalization,其原理是根據信号眼圖的衰減頻率,在特定頻率提高信号的強度,抵消衰減幅額。下(xià)面我們對比了均衡前後的眼圖。

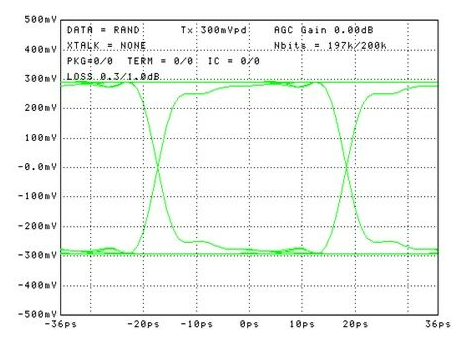

發送端波形

沒開均衡的接收眼圖

打開均衡的接收眼圖

沒開均衡與開均衡後

·PCS(Protocol code sublayer)層編解碼技術(shù)

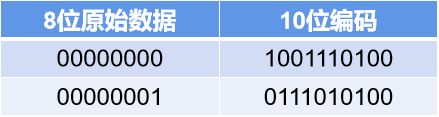

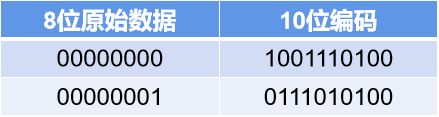

編碼技術(shù)将原始數據插入輔助編碼,提供時鐘修正、塊同步、通(tōng)道綁定和(hé)将帶寬劃等功能,8b/10b編碼是最常用的一種,由IBM開發已經被廣泛采用。8b/10b編碼機制是Infiniband千兆位以太網,也是FiberChannel以及XAUI 10G以太網接口采用的編碼機制。它是一種數值查找類型的編碼機制,可(kě)将8位字轉化為10位符号。這些符号可(kě)以保證有足夠的跳變用于時鐘恢複。

連續的0或者1的情況出現,否則容易導緻很長時間沒有信号跳變而丢失同步信息, 8B/10B編解碼電路(lù)提高了線路(lù)良好的信号穩定性。

針對其他的接口應用,還有4B/5B與64B/66B等編解碼技術(shù),大原理是一樣的,就是插入輔助編碼,提高信号鍊路(lù)的穩定性。

·高速 SerDes 技術(shù)和(hé)各種接口的關(guān)系

随着差分通(tōng)信、時鐘恢複、均衡、編碼等新技術(shù)的實現,串行通(tōng)信這顆老樹(shù)又迎來了新的春天,現在最新的SerDes已經達到了112Gbps傳輸速率,為數字時代的通(tōng)信高速應用,如(rú)大數據存儲、5G通(tōng)信、雲計算、圖形遊戲AI、自動(dòng)駕駛,打下(xià)了堅實基礎!

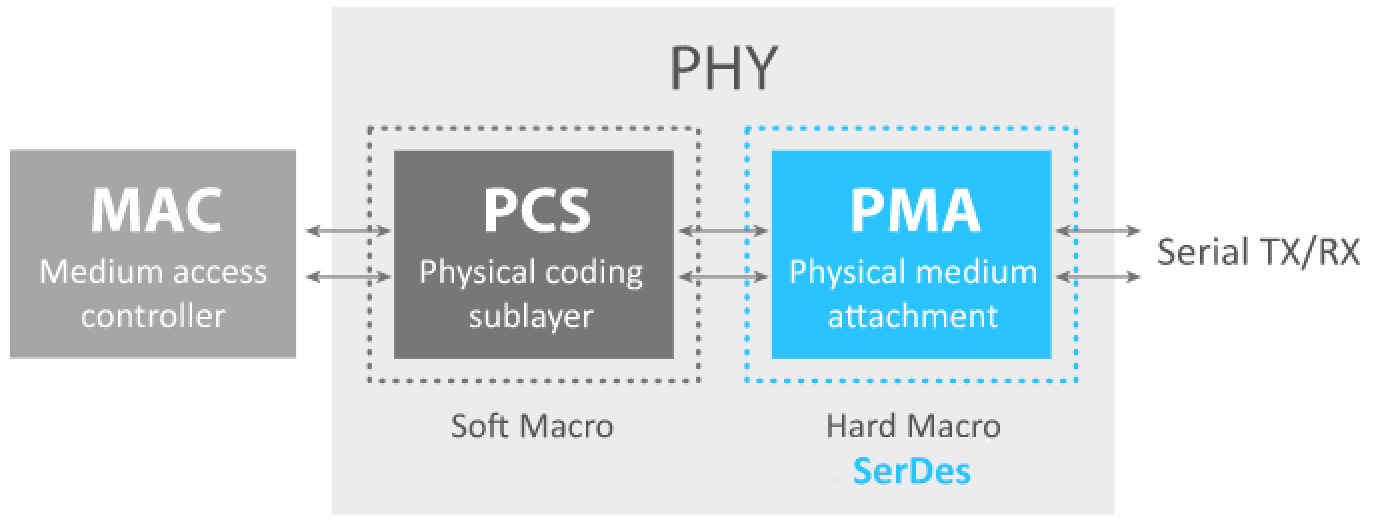

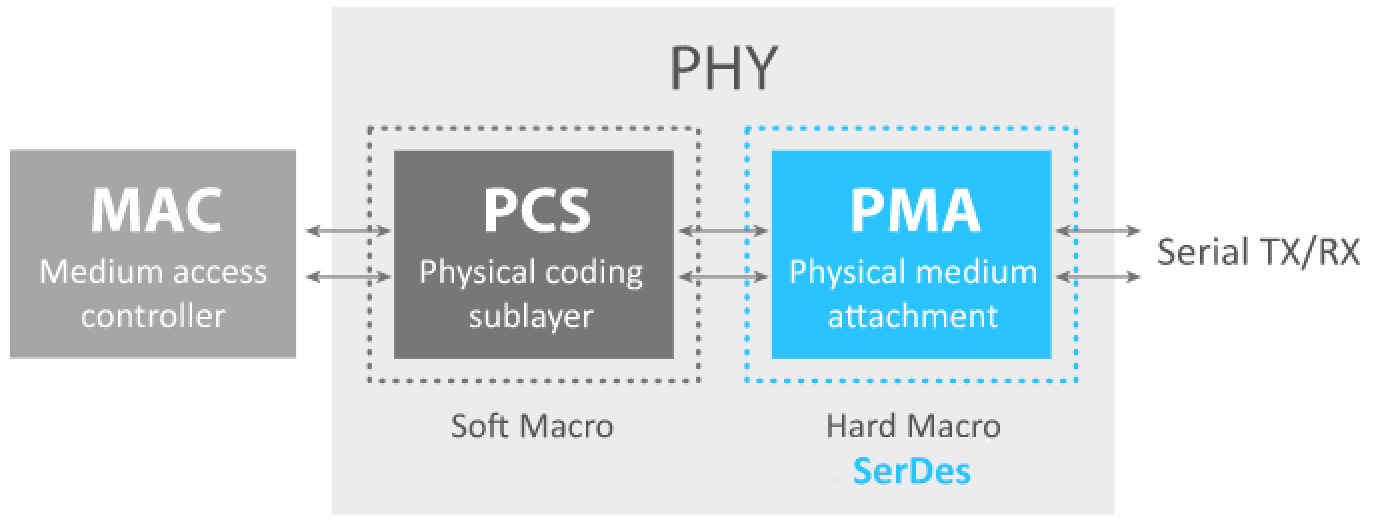

→ PMA - Physical media attachment

差分通(tōng)道,均衡器(qì),串行/解串器(qì)

→ PCS - Protocol code sublayer (針對特定的協議如(rú)PCIE,USB3.0,SATA等進行編碼)

8b/10b編碼解碼,FIFO

經過以上的分析,大家對這幾個(gè)技術(shù)名稱應該有了更深一步的認識,各種我們熟知的高速接口中(zhōng),PCI Express、USB3.0、XAUI萬兆以太網、SATA、DP、RAPID IO、HBM這些高速接口的底層都是基于SerDes技術(shù)。

在接口的模型MAC+PCS+PMA結構,PCS協議層會針對不同的PCIE、USB3.0、XAUI等高速接口,進行差異化編碼,PMA層基本保持一樣,可(kě)以說SerDes技術(shù)是接口技術(shù)科技數的主幹。

四、高速SerDes IP的商(shāng)用狀況

高速SerDes決定了諸多接口技術(shù)的發展,所以各大芯片廠商(shāng)紛紛推出自己的SerDes技術(shù)方案,像Intel、Xilinx、Lattice、TI、NXP、聯發科、海思等都推出了成熟的SerDes方案。瑞芯微、展銳、全志等在國内IP供應商(shāng)的幫助下(xià)也做出很出色的SerDes接口。

這些接口或是自己設計的,或是獲得第三方授權的,各芯片廠商(shāng)并沒有公開自家SerDes接口技術(shù)的來源,我們可(kě)以從IP供應商(shāng)的方向來看看SerDes IP的供應狀況。

第一梯隊的Cadence、Synopsys、Rambus都是美國廠商(shāng),最高做到112Gbps SerDes 多協議PHY。

筆者最近參加了上海國産IP技術(shù)峰會和(hé)蘇州ICDIA集成電路(lù)峰會,仔細學習了各個(gè)主題演講,其中(zhōng)頻頻出現SerDes的關(guān)鍵詞,展現了國内IP廠商(shāng)在SerDes技術(shù)上的努力和(hé)突破,從模仿到自主創新,從本土(tǔ)再到海外,其中(zhōng)聽到最好的消息是以芯動(dòng)科技為首的IP廠商(shāng)很快就要突破112Gbps SerDes技術(shù)。

其實剛聽到這個(gè)消息還是有些驚訝的,印象中(zhōng)本土(tǔ)IP廠商(shāng)的SerDes方案比較少(shǎo),一般是5~8Gbps左右,且集中(zhōng)在40nm老工藝。

芯動(dòng)科技很早就推出了32Gbps SerDes,并且實現了最高5nm的設計實現,這是IP市場上的一個(gè)亮(liàng)點,我在會上特地找芯動(dòng)的SerDes專家了解了他們的發展思路(lù)。

交談中(zhōng)獲悉,IP在追趕國際先進标準過程中(zhōng)需要持續投入巨大的人力和(hé)财力,特别是高速SerDes,工藝尖端的受衆客戶比較少(shǎo)。

芯動(dòng)科技早前就已經排兵(bīng)布局,投入了大量的人才和(hé)資(zī)金疊代技術(shù),因而也成為IP裡最耀眼的新星,這不得不讓人佩服芯動(dòng)科技領導人的眼光和(hé)執行力。

五、芯動(dòng)科技的SerDes IP接口方案和(hé)Innolink

芯動(dòng)成立于2006年,是老牌的IP技術(shù)廠商(shāng),在多個(gè)領域做到第一梯隊,IP種類涵蓋了高性能計算平台,多媒體終端/汽車(chē)電子(zǐ)平台,IoT物聯網平台等。換而言之,芯動(dòng)科技進入市場早、技術(shù)累積早、IP質量穩定,獲得市場認可(kě)、獲得盈利後又投入新的技術(shù)升級,十多年的技術(shù)疊代,腳踏實地拿下(xià)最新5nm設計高地、112Gbps速度巅峰,這并不是資(zī)本市場的新公司靠砸錢就能短(duǎn)時間内堆出來的。

IP技術(shù)需要不斷的累積、技術(shù)疊代,才能更加穩定,芯動(dòng)有超過200次的流片記錄,50億顆授權量産芯片,超過10億顆的高端定制SoC量産,先進工藝到5nm、7nm等。

做過芯片設計的工程師(shī)才知道這些數字有多麼不易,每次流片前,多少(shǎo)個(gè)日日夜夜檢查驗證,生怕出點什麼小差錯,花(huā)了大幾百萬美金做出來的芯片成闆磚,行業(yè)裡流片失敗的慘案簡直不要太多,這個(gè)我就不一一列舉了,大家自己搜索。

從這個(gè)層面上,我理解了大量客戶采用芯動(dòng)IP的原因,芯動(dòng)IP有大量流片驗證經驗,可(kě)以降低風險、加速芯片的流片進度。矽驗證IP是廣大流片設計工程師(shī)的定心丸,特别是先進工藝IP,風險極高,一不小心就會流片失敗翻車(chē)。

仔細翻看市場上的SerDes方案,我發現芯動(dòng)科技不僅在速率上,還在各種接口标準種類、矽驗證覆蓋率等一些重要指标上已經領先。

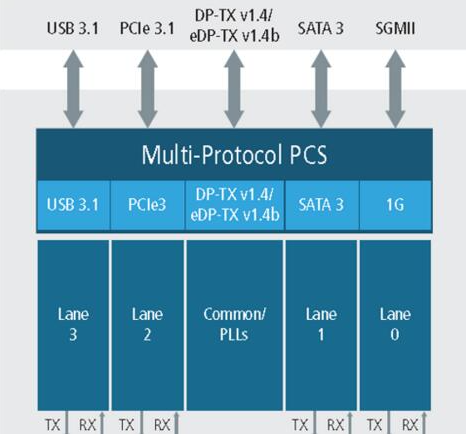

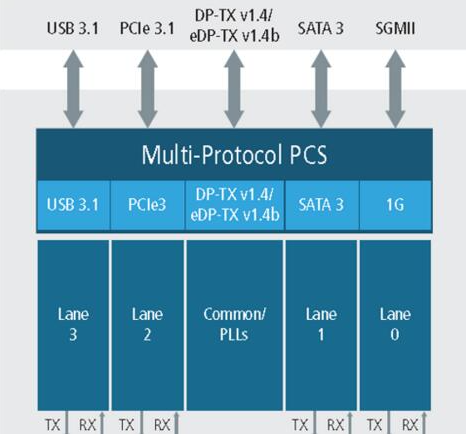

其基于SerDes的高速接口包含了PCIe5 32Gbps、PCIe4/3/2、USB3.1/3.0、SATA,XAUI、SATA、RapidIO、CXL2.0。

這些高速接口,為5G通(tōng)信、自動(dòng)駕駛、人工智能、大數據存儲、雲計算、高性能圖像媒體處理、萬物互聯等應用,打通(tōng)了信息化高速公路(lù)!

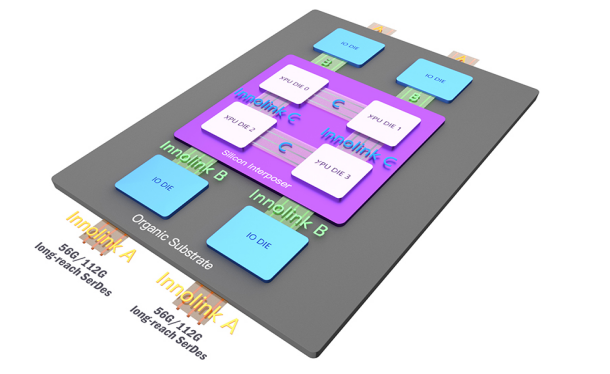

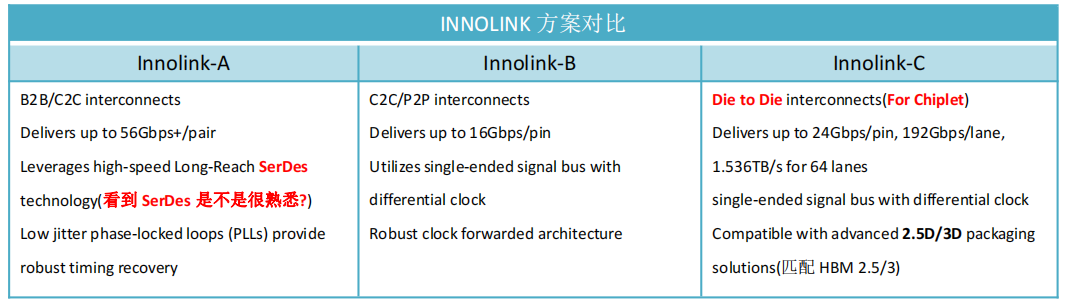

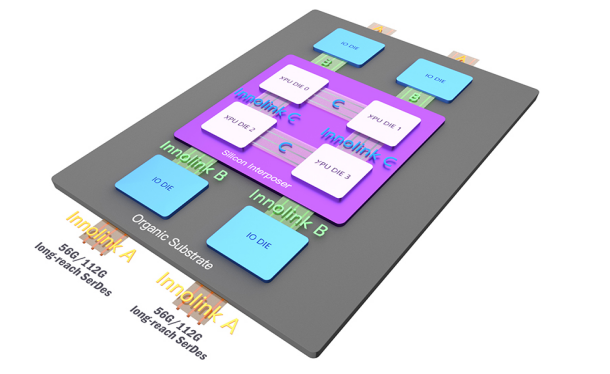

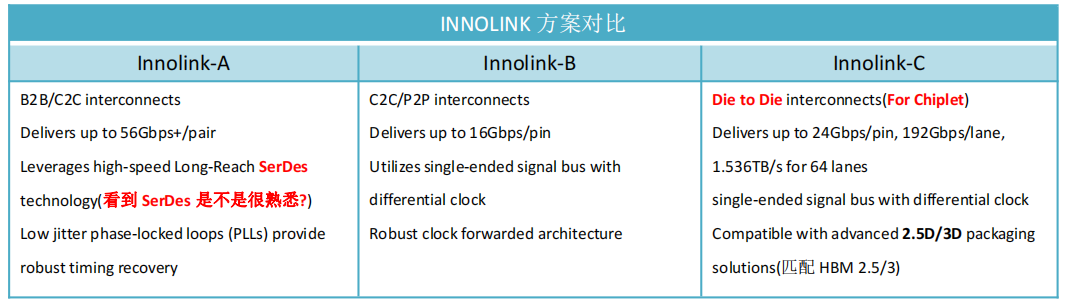

其中(zhōng)Innolink的産品引起了很多技術(shù)專家的興趣,該方案為片内、闆上、闆外提供了3套連接方案,如(rú)下(xià)圖所示,我做了個(gè)歸類:

3種連接方案

3種連接方案

主要包含Chiplet Die-to-Die (D2D),Chip-to-Chip (C2C),Board-to-Board (B2B) 和(hé)Package-to-Package (P2P)等多種連接需求,芯動(dòng)科技布局早,涵蓋了廣泛的應用,其中(zhōng)D2D的Chiplet技術(shù)更是現在摩爾定律延續的新技術(shù),限于篇幅限制,我再另寫文(wén)章介紹。就我看到的,芯動(dòng)15年來一直在做接口IP,有豐富的技術(shù)儲備和(hé)應用經驗,所以能在SerDes技術(shù)的基礎上開發出這套Innolink連接技術(shù),業(yè)界很多專家也對這套IP的量産感興趣,筆者會保持對芯動(dòng)的關(guān)注。

筆者最新獲悉,芯動(dòng)最近發布了首款先進高性能的GPU:風華一号系列,其中(zhōng)就應用了Innolink的技術(shù)。

據悉,風華GPU分為A卡和(hé)B卡,其中(zhōng)B卡是2顆GPU芯片連接組合而成的,低延時的擴展算力和(hé)帶寬給高性能計算、雲應用帶來無限的想象空間,這種黑科技芯動(dòng)自家先用上了,Innolink随着GPU量産背後的意義不言自明,關(guān)于GPU的内容太多,筆者将另起篇章。

從IP的目錄和(hé)量産記錄、工藝節點的覆蓋上,芯動(dòng)已經是市場領先了,順利成章地完成了技術(shù)的積累,為SerDes技術(shù)的發展打下(xià)了基礎,實現了技術(shù)疊代,把握新機遇,這是時代給予廣大芯片企業(yè)的機會,也是芯動(dòng)能抓住這個(gè)風口的原因!

另外芯動(dòng)56Gbps SerDes馬上也要發布了,最新112Gbps據說計劃在2022年初流片了,我們期待芯動(dòng)的高速SerDes IP很快應用到各種數字設備中(zhōng)點亮(liàng)新的通(tōng)信時代。

結束語

本文(wén)淺析了從串口到并口,再到高速SerDes的技術(shù)發展過程,以及SerDes IP廠商(shāng)現狀。芯片公司和(hé)IP廠商(shāng)一起努力,已經在很多技術(shù)節點逐漸突破,取得耀眼的成績,我們每個(gè)半導體人都拭目以待高端芯片的創新發展!

官方公衆号

官方公衆号 招聘公衆号

招聘公衆号